#### 概要

CAT204はZ80互換4倍速CPU KL5C80A12(川崎マイクロエレクトロニクス製)を使用した超小型マイコンボードです。フラッシュROMを実装済みで「バグファインダBF3000」を使用したオンボード・プログラミングとデバックができます。

入出力機能としてRS232を1チャンネルと、パラレル入出力40ビット,パラレル出力16ビットの合計56ビットを使用できます。パラレル出力16ビットは±24mAドライブできます。

尚、本ボードにはバス信号は用意されていませんので、I/0の拡張が必要な場合は、CAT201, CAT202又はCAT68シリーズをお使い下さい。

★注記: CAT204はフラッシュROM書込に「バグファインダBF3000」が必要です。

## 仕様

- ●CPU: KL5C80A12 (川崎マイクロエレクトニクス製)

- ●システムクロック: 7,3728MHz

- ●メモリ:

[プログラム領域] **128KバイトタイプのフラッシュROM実装済み** (SST社製 SST39SF010A又は相当品) 書換え回数は10,000回可能 [データ領域] KL5C80A12内蔵のRAM512バイトを使用 RAMのバッテリ・バックアップはできません

- ●割り込み: CPU内蔵デバイス及び外部入力合計で16レベル KL5C80A12内蔵の割り込みコントローラによるオートベクタ方式

- ●リセット:リセットIC使用、以下の状態でリセット動作パワーON時、5V電圧低下時、マニュアルリセット入力時

- ●シリアルI/0 (KL5C80A12内蔵機能):

RS232レベル 1チャンネル(TxD, RxD信号をサポート)

- ●パラレルI/0 (KL5C80A12内蔵機能):8ビットの汎用I/0×5ポート(40ビット)(パラレルポートはI/0ピンが各種機能と共用です)

- ●増設パラレル出力: 8ビット出力×2ポート(16ビット)

CMOSレベル出力で±24mAドライブ可能

- ●タイマ/カウンタ (KL5C80A12内蔵機能): 16ビットのタイマ/カウンタ×5チャンネル (内1チャンネルはボーレートジェネレータとして使用)

- ●バス信号:用意されていません

必要な場合はCAT201, CAT202, CAT68シリーズをご使用下さい

- ●使用温度範囲:0~55℃ (結露のないこと)

- ●電源:5V±10% 55mA MAX(I/Oからのソース電流は除く)

- ●基板:外形寸法 45×45mm、質量 約15g 基板材質等 FR-4, 1.6t, 4層両面実装基板

## KL5C80A12の資料について

KL5C80A12内蔵機能に関する説明は「KL5C80A12 ハードウェアマニュアル」を参照願います。マニュアルは次のURLからダウンロードできます。

川崎マイクロエレクトロニクス㈱ http://www.k-micro.com/seihin/micon.html

#### コネクタの型番及びピン配列

#### ■ コネクタの配置と型番

コネクタは右図の様に配置されています。(ボードをCPU実装面より見た図です)

CN1の型番:オムロン XG8W-3431 CN2の型番:オムロン

XG8W-3031 CN3の型番:日本圧着端子製造

B6B-EH

#### 【 CN1 】 ピン配列

| 信号名            | ピンNO. |     | 信号名            |

|----------------|-------|-----|----------------|

| MODE1          | 1A    | 1B  | GND            |

| 0P67           | 2A    | 2B  | 0P66           |

| 0P65           | 3A    | 3B  | 0P64           |

| 0P63           | 4A    | 4B  | 0P62           |

| 0P61           | 5A    | 5B  | 0P60           |

| 0P77           | 6A    | 6B  | 0P76           |

| 0P75           | 7A    | 7B  | 0P74           |

| 0P73           | 8A    | 8B  | 0P72           |

| 0P71           | 9A    | 9B  | 0P70           |

| P17/HALT*      | 10A   | 10B | P16/M1*        |

| P15/RXC        | 11A   | 11B | P14/TXC        |

| P13/XCLK1      | 12A   | 12B | P12/GATEA1     |

| P11/XCLK0      | 13A   | 13B | P10/GATEA0     |

| P07/IR7        | 14A   | 14B | P06/IR6        |

| P05/1R5        | 15A   | 15B | P04/1R4        |

| PO3/IR3/NMI*   | 16A   | 16B | P02/IR2/GATEB2 |

| P01/IR1/GATEB1 | 17A   | 17B | P00/IR0/GATEB0 |

・MODE1ピンをLOWにするとBoot-on-RAMモードになります。HI又は オープンでノーマルモードです。

#### 【 CN2 】ピン配列

| 信号名        | ピンNO. |     | 信号名        |

|------------|-------|-----|------------|

| P47/SYNDBD | 1A    | 1B  | P46/RTS*   |

| P45/DTR*   | 2A    | 2B  | P44/BACK*  |

| P43/SYDTIN | 3A    | 3B  | P42CTS*    |

| P41/DSR*   | 4A    | 4B  | P40/BREQ*  |

| P37/OUTBS2 | 5A    | 5B  | P36/OUTBP0 |

| P35/0UTA1  | 6A    | 6B  | P34/0UTA0  |

| P33/0UTBP2 | 7A    | 7B  | P32/OUTBP1 |

| P31/SYNC   | 8A    | 8B  | P30/OUTBS0 |

| P27        | 9A    | 9B  | P26        |

| P25        | 10A   | 10B | P24        |

| P23        | 11A   | 11B | P22        |

| P21        | 12A   | 12B | P20        |

| TXD        | 13A   | 13B | RXD        |

| GND        | 14A   | 14B | GND        |

| 5V         | 15A   | 15B | 5V         |

#### 【 CN3 】バグファインダ接続コネクタのピン配列及び機能

| ピンNo. | 信号名    | 機能                      |  |  |  |

|-------|--------|-------------------------|--|--|--|

| 1     | BFS10  | バグファインダ用の双方向シリアル信号      |  |  |  |

| 2     | CLK    | バグファインダ用クロック信号出力        |  |  |  |

| 3     | 5V     | - バグファインダ用5V電源出力        |  |  |  |

| 4     | GND    |                         |  |  |  |

| 5     | RESET* | リセット入力(RESETをLowレベルにすると |  |  |  |

| 6     | GND    | CAT204はリセット状態になります)     |  |  |  |

#### メモリ

## ●プログラム領域メモリの設定

プログラムメモリとして128KバイトのフラッシュROMが実装済みです。KL5C80A12内蔵のシステム制御レジスタ(SCR1)の、外部バス・ウェイト・コントロールは外部メモリの全て(00000~FFDFF)をOwaitに設定します。この時、外部I/Oウェイトは1waitになります。

SCR1<D7:D0> = [ 11XX XXXX ] フラッシュROMの物理アドレス:00000H~1FFFFH

#### ●データ領域メモリの設定

データ領域のメモリはKL5C80A12の内蔵RAM512バイトを使用します。設定項目はありません。

RAMの物理アドレス:FFE00H~FFFFFH

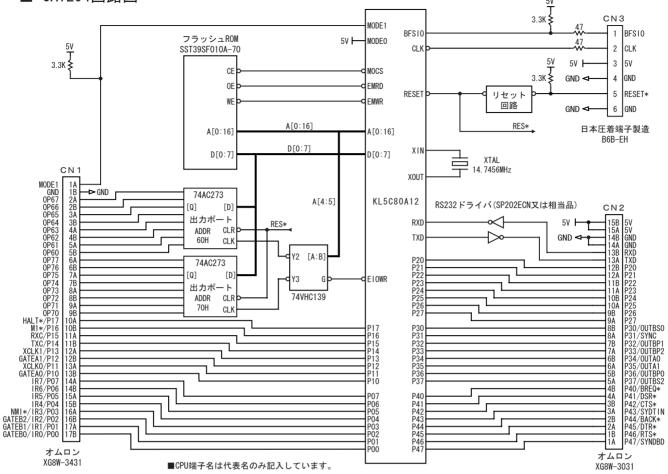

## ■ CAT204回路図

#### ●MMUの設定

リセット時、64Kバイトの論理メモリ空間は全てプログラム領域 (フラッシュROM)に割り付けられて、RAMが使用できない状態になり ますので、プログラムの最初でMMUの設定を行って、RAMを有効にす る必要があります。以下にプログラム領域として60Kバイト、デー タ領域として4Kバイトを割付けるMMUの設定例を示します。

(但しCAT204が実装しているRAMは、KL5C80A12内蔵の512バイトのみですので、使用可能なRAMは論理アドレスFE00H~FFFFHの512バイ トになります。)

;RO領域 = フラッシュROM 論理アドレス0000H~EFFFH (物理アドレス00000H~0EFFFH)

論理アドレスFE00H~FFFFH :R4領域 = CPU内蔵RAM (物理アドレスFFE00H~FFFFFH)

A. 03BH ;R1, R2, R3領域は使用しない LD OUT (06H), A ;MMUのBBR4レジスタに3BHを設定

### 1/0

KL5C80A12内蔵のシリアルI/OのTXDとRXDがRS232レベルで使用で きます。RTS,CTS等を使用する場合は、外部にRS232ドライバICを用意してください。

#### ●CPU内蔵パラレルI/0

8ビットのパラレルI/Oが5ポートあり、KL5C80A12の信号がそのま まコネクタに接続されています。ボード上でプルアップ、プルダウ ンはしていません。(但し、CPU内で全てのI/Oがプルアップされて います)

#### ●増設パラレル出力(OP60~P67、OP70~P77)

8ビットの出力専用ポートを2ポート実装しています。出力ICに 74AC273を使用しており、出力電流は最大で±24mAまでドライブで きます。リセット時に出力は全てLOWレベルになります。 尚、このポートからのデータ読み出しはできません。

#### ● I /Oアドレス

- ・出力専用ポートOP6のアドレスは60Hです。(61~6FH, A0~AFH, E0 ~EFHにはイメージがでます)

- ・出力専用ポートOP7のアドレスは70Hです。(71~7FH, BO~BFH, FO ~FFHにはイメージがでます)

- ・KL5C80A12内蔵のI/Oアドレスについては「KL5C80A12ハードウェ アマニュアル」を参照下さい。

## リセット・フラッシュROM書き込み

#### ●リセット

リセットICにより以下の条件でリセット状態になります。リセッ ト状態はリセット発生条件解除後、約200mSec間保持されます。

- ・パワーONリセット:電源投入時に発生

- ・電圧低下:5Vラインが約4.2V以下になった時に発生

- ・外部リセット入力: CN3のRESET信号をLOWレベルにした時に発生

#### ●フラッシュROMの書き込み

本ボードにはTSOPパッケージのフラッシュROMが実装済みで、取 り外しはできません。このフラッシュROMへのプログラム書き込み には、バグファインダ「BF3000」が必要です。

バグファインダ「BF3000」は、バグファインダに付属のケーブル で、本ボード上のコネクタCN3に直接接続できます。

(注記:他社製のバグファインダは、フラッシュROM書き込み機能が 無いので使用できません)

# 注意!! 本製品を不適切な状態で使用されますと、発火等の可能性があり危険です。

- ■仕様範囲外の電圧を加えたり、過負荷で使用しないで下さい

- ■サージ,ノイズ等が本製品に加わらない様、十分なノイズ対策を行なって下さい。

- ■本製品は人命にかかわる状況や、極めて高い信頼性が要求される用途を目的として 設計・製造されたものではありません。

# エーワン株式会社

〒486-0852 愛知県春日井市下市場町6-9-20 TEL/FAX: 0568-85-8511/8501 URL: http://www.aone.co.jp/cat