# 2軸モータコントロールボード

# CAT68007 PMC-2

# 取扱説明書

1998, 02, 25 - 2002, 09, 03

## 【1】概要

CAT68007 PMC-2 はコントロール IC に日本パルスモーター社製の PCL-240MK を使用した 2 軸位置決め制御ボードです。

パルスモータはもちろんパルス列入力タイプのサーボドライバを使用することにより AC 及び DC サーボモータの位置決め制御も簡単に行うことができます。各軸にはフォトカプラでアイソレーションされたリミット SW 入力やバッファされた指令パルス出力などが備わっています。代表的な動作例として次のようなものがあります。

- ●即停止

- ●減速停止

- ●高速連続動作(加減速あり)

- ●定速連続動作

- ●高速プリセット動作(加減速あり)

- ●定速プリセット動作

- ●高速原点復帰動作(加減速あり)

- ●定谏原点復帰動作

## 【2】仕様

●制御 IC: PCL-240MK (日本パルスモーター社製)

●制御軸:2軸(本ボードを複数枚使用して多軸制御もできます)

●最大送り速度:240Kpps (基準クロック 4.9152MHz)

●出力パルス数設定範囲:1~16777215パルス

●加減速制御:直線加減速(スローダウンポイント自動設定)

●加減速時間設定範囲: 3.3msec ~ 27.3sec

●現在位置カウンタ:

24bit アップダウンカウンタにより指令パルス出力、またはエンコーダ入力信号をカウント

●リミット入力信号:

フォトカプラによるアイソレーション入力 (入力電流 10mA/24V)

EL+, EL-: ストロークエンド SD : 減速リミット ORG : 原点リミット

●エンコーダ入力信号:

高速フォトカプラによるアイソレーション入力(入力電流  $6.5 \sim 12 mA$ )

A+, A- : A 相入力 B+, B- : B 相入力 Z+, Z- : Z 相入力

●ドライバステータス入力信号:

フォトカプラによるアイソレーション入力(入力電流 10mA/24V)

ALM: アラーム信号入力INP: インポジション入力

●指令パルス出力信号:

オープンコレクタ出力及びラインドライバによる差動出力

・オープンコレクタ出力(出力定格 最大 30V/40mA)

POUT : (+) パルス出力, (又は共通パルス出力)

PDIR : (-) パルス出力, (又は方向信号出力)

・ラインドライバによる差動出力(RS-422 レベル)

POUT+, POUT : (+) パルス出力, (又は共通パルス出力)

PDIR+, PDIR : (-) パルス出力, (又は方向信号出力)

●ドライバコントロール出力信号:

フォトカプラによるアイソレーション出力 (出力定格 最大 30V/30mA)

ECL: 偏差カウンタクリア出力SON: サーボ ON 出力 (汎用出力)

#### ●割り込み:

原点復帰動作の完了時、エンドリミットによる停止時などの場合、 PCL-240MKより割込みを発生

●バスバッファ: TD74BC645 及び相当品でバッファ

●使用温度範囲:0~55℃●電源:+5V ±5% MAX 300mA

●重量:約100g

●基板:

基板寸法 120 × 128 (コネクタ等、突起部分は含まない) 基板材質 ガラス布基材エポキシ樹脂 1.6t 4層基板

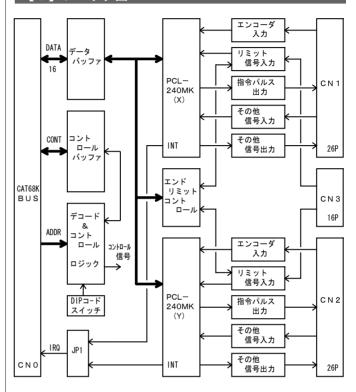

## 【3】ブロック図

# 【4】 I /Oアドレスの設定

■ 16/32 ビット CPU を使用している場合

アドレス信号の  $A8\sim A11$  を DIP コードスイッチで選択して I/0 アドレスを設定します。スイッチを指先で回して希望のアドレス番号と  $\triangle$ 印を合わせて下さい。 アドレスの下位 8 ビット  $(A0\sim A7)$  は固定

本品を合わせて下さい。 アドレスの下位 8 とッド (AU ~ AT) は固定になっており変更できません。また、アドレスの上位 (A12 以上) は、組合せて使用する CPU ボードにより決まりますので使用する CPU ボードの説明書を参照して下さい。

| A12以上     | A11~A8                     | A7~A0                | 選択内容                              |

|-----------|----------------------------|----------------------|-----------------------------------|

| MIZ以上     | ATTIVAO                    | A7. AU               | <b>进队内</b> 台                      |

|           | O~F<br>PUポート゚<br>で固定<br>選択 | 20~FF                | 本ボードでは使用していません                    |

|           |                            | 18~1F                | I/Oの割り付けはありませんが<br>/DTACK信号が返されます |

| CDII+, I, |                            | 12~17<br>の奇数<br>アドレス | 11番地のイメージ                         |

|           |                            | 11                   | エンドリミットコントロールポート                  |

| CEL       |                            | 0F                   | Y軸PCL240MKデータレジスタ(ビット23~16)入出力    |

|           |                            | OD                   | Y軸PCL240MKデータレジスタ(ビット15~08)入出力    |

|           |                            | 0B                   | Y軸PCL240MKデータレジスタ(ビット07~00)入出力    |

|           |                            | 09                   | Y軸PCL240MKステータス入力・コマンド設定          |

|           |                            | 07                   | X軸PCL240MKデータレジスタ(ビット23~16)入出力    |

|           |                            | 05                   | X軸PCL240MKデータレジスタ(ビット15~08)入出力    |

|           |                            | 03                   | X軸PCL240MKデータレジスタ(ビット07~00)入出力    |

|           |                            | 01                   | X軸PCL240MKステータス入力・コマンド設定          |

●偶数アドレス(データバスの上位バイトD8~D15)は使用していません。

## ■ 8 ビット CPU を使用している場合

アドレス信号の  $A4 \sim A7$  を DIP コードスイッチで選択して I/0 アドレスを設定します。スイッチを指先で回して希望のアドレス番号と  $\blacktriangle$ 印を合わせて下さい。アドレスの下位 4 ビット ( $A0 \sim A3$ ) は固定になっており変更できません。

| A7~A4       | A3~A0 | 選択内容                           |

|-------------|-------|--------------------------------|

|             | (固定)  | ~*****                         |

|             | E     | Y軸PCL240MKデータレジスタ(ビット23~16)入出力 |

|             | С     | Y軸PCL240MKデータレジスタ(ビット15~08)入出力 |

|             | A     | Y軸PCL240MKデータレジスタ(ビット07~00)入出力 |

| 0 ~ F       | 8     | Y軸PCL240MKステータス入力・コマンド設定       |

| スイッチで<br>選択 | 6     | X軸PCL240MKデータレジスタ(ビット23~16)入出力 |

| <b>运</b> 1八 | 4     | X軸PCL240MKデータレジスタ(ビット15~08)入出力 |

|             | 2     | X軸PCL240MKデータレジスタ(ビット07~00)入出力 |

|             | 0     | X軸PCL240MKステータス入力・コマンド設定       |

・X0~XF番地内の奇数アドレスは使用していません。

# ●アドレス設定例

- 16/32ビットCPUボード使用時 (CAT68201を使用した時の例) スイッチの設定が左図の時アドレスは 00400B01H~00400B11Hになります。

- 8ビットCPU使用時 スイッチの設定が左図の時アドレスは BOH~BEHになります。

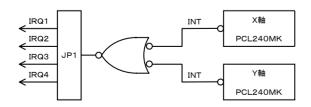

# 【<u>5</u>】割込みについて

原点復帰動作の完了時やエンドリミットによる停止時などに PCL-240MK の INT 出力ピンより割込を発生させることができます。このボードでは PCL-240MK を 2 個実装していますので、各 IC の INT 出力は 0R されてジャンパ [JP1] で選択した割り込み要求信号 (IRQ1  $\sim$  IRQ4) に接続されます。

尚、PCL-240MKに INT リセットコマンドを与えることにより、割り込み要求をクリアすることができます。

# [JP1]割り込みレベル選択

| ジャンパ番号 | 割り込みレベル |

|--------|---------|

| 1      | IRQ1    |

| 2      | IRQ2    |

| 3      | IRQ3    |

| 4      | IRQ4    |

| ジャンパ無し | 割り込み無し  |

例1) 例2) 割り込みを IRQ3で 使用しない 割り込みを 場合 使用する場合 [JP1] [JP1] 1 🗆 🗆 1 🗆 🗆 2 00 2 🗆 🗆 3 3 4 🗆 🗆 4 🗆 🗆

(ジャンパ無し) (3をジャンパ)

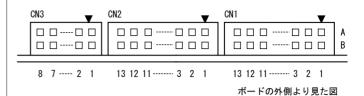

# 【6】入出カコネクタのピン配列及び型番

#### ●入出力コネクタのピン配列

[CN1] [CN2]

| [0111] |       |     |        |  |

|--------|-------|-----|--------|--|

| 信号名    | ピンNo. |     | 信号名    |  |

| 5V     | 1A    | 1B  | XPOUT  |  |

| 5V(R)  | 2A    | 2B  | GND    |  |

| 5V     | ЗА    | 3B  | XPDIR  |  |

| 5V(R)  | 4A    | 4B  | GND    |  |

| XSON   | 5A    | 5B  | XECL   |  |

| XALM   | 6A    | 6B  | XINP   |  |

| GND    | 7A    | 7B  | GND    |  |

| XPOUT+ | 8A    | 8B  | XPOUT- |  |

| XPDIR+ | 9A    | 9B  | XPDIR- |  |

| XA+    | 10A   | 10B | XA-    |  |

| XB+    | 11A   | 11B | XB-    |  |

| XZ+    | 12A   | 12B | XZ-    |  |

| 5V     | 13A   | 13B | GND    |  |

|        | [CN2] |     |        |  |  |

|--------|-------|-----|--------|--|--|

| 信号名    | ピンNo. |     | 信号名    |  |  |

| 5V     | 1A    | 1B  | YPOUT  |  |  |

| 5V(R)  | 2A    | 2B  | GND    |  |  |

| 5V     | 3A    | 3B  | YPDIR  |  |  |

| 5V(R)  | 4A    | 4B  | GND    |  |  |

| YSON   | 5A    | 5B  | YECL   |  |  |

| YALM   | 6A    | 6B  | YINP   |  |  |

| GND    | 7A    | 7B  | GND    |  |  |

| YPOUT+ | 8A    | 8B  | YPOUT- |  |  |

| YPDIR+ | 9A    | 9B  | YPDIR- |  |  |

| YA+    | 10A   | 10B | YA-    |  |  |

| YB+    | 11A   | 11B | YB-    |  |  |

| YZ+    | 12A   | 12B | YZ-    |  |  |

| 5V     | 13A   | 13B | GND    |  |  |

- ・5V:5Vが外部に出力されています。

- ・GND:5Vのグラウンドです。システムグラウンドと接続されています。

## [CN3]

| 信号名  | ピンNo. |    | 信号名  |

|------|-------|----|------|

| 24V  | 1A    | 1B | 24V  |

| G24  | 2A    | 2B | G24  |

| XEL+ | 3A    | 3B | XEL- |

| XSD  | 4A    | 4B | XORG |

| YEL+ | 5A    | 5B | YEL- |

| YSD  | 6A    | 6B | YORG |

| N. C | 7A    | 7B | N. C |

| N. C | 8A    | 8B | N. C |

- -24V:外部電源の24Vです。外部から供給して下さい。

- ・G24V:24Vのグラウンドです。システムグラウンドとは接続されていません。

## ●入出力コネクタの型番 (オムロン製)

| 名 称                | CN1, CN2型番  | CN3型番       | 備考     |

|--------------------|-------------|-------------|--------|

| ヘッダー (基板側)         | XG4C-2634   | XG4C-1634   |        |

| ソケット + ストレインリリーフ   | XG4M-2630-T | XG4M-1630-T | 付属品    |

| 2列ソケット (バラ線圧接用)    | XG5M-2632-N | XG5M-1632-N | AWG24用 |

| セミカバー (バラ線圧接用)     | XG5S-1301   | XG5S-0801   |        |

| ロックレバー (バラ線フラット共用) | XG4Z-       | -0002       |        |

# 【7】入出力信号の説明(CN1, CN2, CN3)

ここでの各種信号の説明は、入出力コネクタ (CN1, CN2, CN3) 表に記載してある信号名称に従って書いてあり、先頭のアルファベット (X, Y)で2軸を区別しています。信号名の2文字目からは両軸共通の名称になっていますので、以下の説明は先頭の文字を除いた信号名で書いてあります。尚、ここではインターフェイス部分及び信号機能の簡単な説明のみが記述されていますので、信号の詳しい説明とICの使用方法の詳細はつぎの資料によりご確認ください。

日本パルスモーター (株) TEL 03-3813-8841

『 高速パルスジェネレータ PCL-240MK ユーザーズマニュアル 』

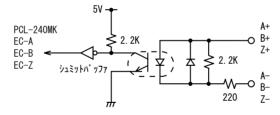

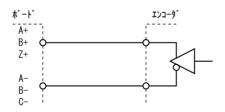

## <7-1> エンコーダ入力信号 (CN1, CN2)

#### ● [ A+, A- ]、[ B+, B- ]

- 現在位置カウンタのカウントを外部エンコーダ信号入力より行う ときに使用します。

- ・この信号はそれぞれ PCL-240MK の EC-A 端子 , EC-B 端子へ入力され ており、PCL-240MK の設定により " 逓倍なし "、"2 逓倍 "、"4 逓倍 "、"2 パルス入力 " の選択ができます。

- ・2パルス入力モード時には [A+, A-] に (+) カウント信号を、[B+, B-] に (-) カウント信号を入力します。

#### ● [ Z+, Z- ]

- ・原点復帰動作完了にエンコーダの Z 相信号を使うときに使用します。

- ・この信号はPCL-240MKのEC-Z端子へ入力されています。また、PCL-240MKのINS端子(汎用入力)にも入力されていますので [Z+, Z-] 信号をCPUから読むこともできます。

#### ●インターフェース回路

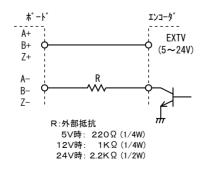

エンコーダ入力信号は高速フォトカプラでインターフェイスされて おり、差動ラインドライバまたはオープンコレクタ出力を接続する ことができます。オープンコレクタで使用するときは外部に電流制 限抵抗を接続する必要があります。

フォトカプラが通電している時に PCL-240MK の各入力端子 (EC-A, EC-B, EC-Z) は、Hi レベルになります。フォトカプラが非通電の時 Low レベルになります。

#### ●接続例

・差動ラインドライバでのインターフェース

・オープンコレクタでのインターフェース

# <7-2>リミット入力信号(CN3)

#### ● 「 ORG ]

- ・原点リミットスイッチの入力用で、PCL-240MK の ORG 端子に入力してあります。

- ・PCL-240MK の制御モードセレクトで ORG 有効 (原点復帰モード) と したときに、この信号が入ると停止します。

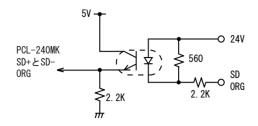

#### ● [ SD ]

- ・スローダウンリミットスイッチの入力用で、PCL-240MK の SD+ 端子と SD- 端子の両方に入力してありますので動作方向に関係なく使用できます。

- ・PCL-240MK の制御モードコマンドで SD 有効としたときにこの信号 が入るとスローダウンします。

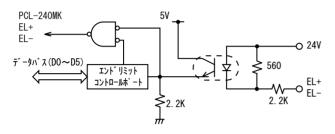

# • [ EL+ ], [ EL- ]

- ・エンドリミットスイッチの入力用で、エンドリミット有効 / 禁止 回路を通して PCL-240MK の EL+ 端子と EL- 端子に、それぞれ入力 してあります。

- ・動作方向と同一方向のEL信号が入力したとき停止します。

#### ■エンドリミット入力の有効 / 禁止設定

エンドリミットコントロールポートを設定することにより PCL-240MK へのエンドリミット入力 (EL+, EL-) を禁止することができます。また、エンドリミットの状態を PCL-240MK を介さずに直接このポートから読み込めます。

エンドリミットコントロールポート

| ピット | WRITE                  | READ           |

|-----|------------------------|----------------|

| D7  | 未使用                    | 不定             |

| D6  | 未使用                    | 不定             |

| D5  | Y軸[EL+], [EL-]有効/禁止の設定 | Y軸有効/禁止設定の読み込み |

| D4  | X軸[EL+], [EL-]有効/禁止の設定 | X軸有効/禁止設定の読み込み |

| D3  | 未使用                    | Y軸[EL-]信号の読み込み |

| D2  | 未使用                    | Y軸[EL+]信号の読み込み |

| D1  | 未使用                    | X軸[EL-]信号の読み込み |

| D0  | 未使用                    | X軸[EL+]信号の読み込み |

# ・設定

PCL-240MK へのエンドリミット入力 [EL+]、[EL-] を禁止する場合、コントロールポートのビット D4(X 軸)、D5(Y 軸) に "1" を書き込み、有効にする場合は "0" を書き込みます。D4,D5以外のビットは使用していませんので "0"、"1" どちらでも構いません。X 軸、Y 軸個別に設定することができます。尚、パワー ON 等のリセット時にはエンドリミット入力は有効に設定されます。

#### ・蒜み出1

ビット D4、D5 からは、設定した値 (0:有効、1:禁止) が読み出せます。 ビット D3  $\sim$  D0 からは、エンドリミットスイッチ入力 [EL+]、[EL-] の状態を常に読み出すことがができます。 [EL+]、[EL-] 入力が非通電のとき "0" が読み込まれ、通電状態のとき "1" が読み込まれます。

#### (注記

エンドリミットコントロールの機能は、8 ビット CPU 使用時には使えません。16 ビット CPU 使用時に有効になります。8 ビット CPU 使用時には、PCL-240MK へのエンドリミット入力は常に有効になります。

#### ●インターフェース回路

リミット入力信号はフォトカプラでインターフェースされています。フォトカプラが通電状態のとき PCL-240MK の各入力端子 (ORG, SD+, SD-, EL+, EL-) は hi レベルになり、非通電のとき low レベルになります。 (PCL-240MK は、これらの入力信号を負論理で扱いますのでリミットスイッチは B 接点を使って下さい)

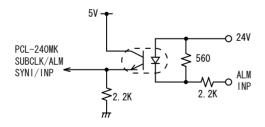

# <7-3>ドライバステータス入力信号(CN1, CN2)

#### ● [ ALM ]

- ・アラーム入力信号で、PCL-240MK の SUBCLK/ALM 端子に入力されています。

- ・この信号で PCL-240MK からのパルス出力を強制停止することができます。 論理はプログラムにより負論理または正論理のどちらでも設定できます。

# • [ INP ]

- ・サーボドライバからのインポジション入力信号で、PCL-240MKの SYNI/INP端子に入力されています。

- ・PCL-240MK からのパルス出力が完了しても、サーボドライバからこの信号が入力されるまで INT 信号は出力されません。論理はプログラムにより負論理または正論理のどちらでも設定できます。

# ●インターフェース回路

[ALM]、[INP] 信号はフォトカプラでインターフェースされており、フォトカプラが通電状態のとき PCL-240MK の各入力端子 (SUBCLK/ALM, SYNI/INP) は Hi レベルになり、非通電のとき Low レベルになります。

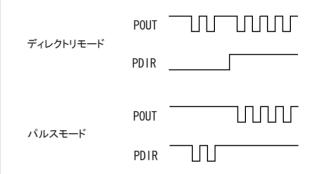

# <7-4> 指令パルス出力信号 (CN1, CN2)

[ POUT+, POUT- ], [ PDIR+, PDIR- ]

- ・パルス (サーボ)モータドライバへのパルス出力信号で、PCL240MK の (POUT, PDIR) 端子からドライバを通して出力されています。

- ・PCL-240MK の出力モードセレクトにより方向信号, 共通パルス出力 (ディレクトリモード)と、(+)パルス,(-)パルス出力(パルスモード)とが切り替えれます。

#### [ POUT+, POUT- ]

ディレクトリモード時 : 共通パルス出力 パルスモード時 : (+)方向パルス出力

#### [ PDIR+, PDIR- ]

ディレクトリモード時 : 方向信号出力 パルスモード時 : (-) 方向パルス出力

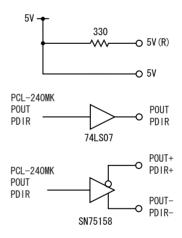

#### ●インターフェース回路

オープンコレクタ出力、差動ドライバ出力の2種類が出力されています。この信号はシステムGNDとアイソレーションされていません。

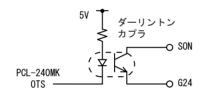

#### ● [ SON ]

•PCL-240MK の OTS 端子からフォトカプラを通して出力されています。 モータドライバの ON/OFF 信号として使用できます。PCL-240MK の OTS 信号は汎用の出力信号ですので、他の目的に使用しても構いま せん。

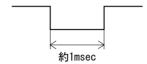

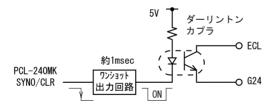

# • [ ECL ]

- ・PCL-240MK の SYNO/CLR 出力信号をワンショット回路を通して約 1mSEC のパルスを作っており、SYNO/CLR 信号の立ち下がり時から 約 1mSEC 間パルスが出力されます。(この信号を出力後のサーボドライバへの司令パルス出力は 1mSEC の時間を考慮する必要があります)

- ・この信号はサーボドライバの偏差カウンタをクリアするための信号です。 原点復帰完了時、またはマニュアル制御により出力できます。

## ●インターフェース回路

[SON]、[ECL] 信号はダーリントンフォトカプラを通して出力されています。

[SON] 出力信号は PCL-240MK の OTS 出力を 1ow レベルにした時に、出力フォトカプラが "ON" になります。

[ECL] 出力信号は PCL-240MK の SYNO/CLR 信号出力の立ち下がり時から 約 1mSEC 間、出力フォトカプラが "ON" になります。

# ⚠ 注意

本製品は取扱いを間違えたり不適切な状態で使用されますと部品が破損したり、発火する可能性があり危険ですので以下の注意事項を必ずお守り下さい。

- ●電源の極性を逆に接続したり、使用範囲外の電圧を加えたりしないで下さい。

- ●各種出力信号、入出力双方向信号を電源やグランドに直接接続したり、過負荷で使用しないで下さい。 (必ず適正な負荷範囲内で使用して下さい。)

- ●サージ電圧、ノイズ等の発生が予想される機器、部品等の近くで使用する場合は、発生源に十分なノイズ対策を 行って下さい。

- ●本製品は部品や部品のリード線がそのまま露出していますので指などに怪我をしないように取扱いには注意して下さい。

- ●当社製品は、人命にかかわるような状況下や、極めて高い信頼性が要求される用途の製品・設備に組込まれることを目的として設計・製造されたものではありません。

エーワン株式会社 FAX(0568)85-8501 http://www.aone.co.jp/cat/ 〒 486-0852 愛知県春日井市下市場町 6-9-20