|

1.ユーザ側での準備項目 |

| 【ピン設定】 |

| ・ |

[JTAG]デバッグ機能選択端子[EMLE:HIGH][UB:LOW]レベルにした時にデバッグ可能になります。 |

| ・ |

[FINE]デバッグ機能選択端子[EMLE:LOW][UB:LOW]レベルにした時にデバッグ可能になります。 |

| ・ |

[BOOT]デバッグ機能選択端子[EMLE:LOW][MD:LOW][UB:LOW]レベルにした時にブート接続が可能になります。 |

| 【コールドスタート】 |

| ・ |

JTAG/FINEモードの接続時にターゲット側を初期化後エミュレーションモードに遷移しリセット値で停止する機能です。 |

| 【ホットスタート】 |

| ・ |

JTAGモードの接続時にターゲット側を初期化しないで実行を保持したまま起動する機能です。 |

| ・ |

ホットスタートモードの確認中は、AH8000起動状態でターゲット基板とケーブル接続した状態で確認して下さい。 |

| ・ |

コントロールソフトDEF8Kはクローズ状態でも構いません。 |

| 【ライブデバッグ】 |

| ・ |

FINEモードの接続時にターゲット側を初期化しないで実行を保持したまま起動する機能です。 |

| ・ |

LiveDebugモードの確認中は、AH8000起動状態でターゲット基板とケーブル接続した状態で確認して下さい。 |

| ・ |

コントロールソフトDEF8Kはクローズ状態でも構いません。 |

| 【メモリマップ】 |

|

| グループ |

品種

|

内蔵ROM開始 |

内蔵RAM終了 |

ファーム使用 |

デバッグモード |

| RX210 |

R5F52105 |

0xFFFE_0000(128KB) |

0x04FFF(20KB) |

0x84000(8KB) |

FINE/BOOT |

| |

R5F52106 |

0xFFFC_0000(256KB) |

0x07FFF(32KB) |

0x84000(8KB) |

FINE/BOOT |

| |

R5F52107

|

0xFFFA_0000(384KB) |

0x0FFFF(64KB) |

0x84000(8KB) |

FINE/BOOT |

| |

R5F52108 |

0xFFF8_0000(512KB) |

0x0FFFF(64KB) |

0x84000(8KB) |

FINE/BOOT |

| RX230 |

R5F52305 |

0xFFFE_0000(128KB) |

0x07FFF(32KB) |

0x84000(8KB) |

FINE/BOOT |

| |

R5F52306 |

0xFFFC_0000(256KB) |

0x07FFF(32KB) |

0x84000(8KB) |

FINE/BOOT |

| RX231 |

R5F52315 |

0xFFFE_0000(128KB) |

0x07FFF(32KB) |

0x84000(8KB) |

FINE/BOOT |

| |

R5F52316 |

0xFFFC_0000(256KB) |

0x07FFF(32KB) |

0x84000(8KB) |

FINE/BOOT |

| |

R5F52317 |

0xFFFA_0000(384KB) |

0x0FFFF(64KB) |

0x84000(8KB) |

FINE/BOOT |

| |

R5F52318 |

0xFFF8_0000(512KB) |

0x0FFFF(64KB) |

0x84000(8KB) |

FINE/BOOT |

| RX23T |

R5F523T3 |

0xFFFF_0000(64KB) |

0x027FF(10KB) |

0x84000(8KB) |

FINE/BOOT |

| |

R5F523T5 |

0xFFFE_0000(128KB) |

0x027FF(10KB) |

0x84000(8KB) |

FINE/BOOT |

| RX621 |

R5F56216 |

0xFFFC_0000(256KB) |

0x0FFFF(64KB) |

0x84000(8KB) |

JTAG/BOOT |

| |

R5F56217 |

0xFFFA_0000(384KB) |

0x0FFFF(64KB) |

0x84000(8KB) |

JTAG/BOOT |

| |

R5F56218 |

0xFFF8_0000(512KB) |

0x17FFF(96KB) |

0x84000(8KB) |

JTAG/BOOT |

| RX62N |

R5F562N7 |

0xFFFA_0000(384KB) |

0x0FFFF(64KB) |

0x84000(8KB) |

JTAG/BOOT |

| |

R5F562N8 |

0xFFF8_0000(512KB) |

0x17FFF(96KB) |

0x84000(8KB) |

JTAG/BOOT |

| RX62T |

R5F562T6 |

0xFFFF_0000(64KB) |

0x01FFF(8KB) |

0x84000(8KB) |

JTAG/BOOT |

| |

R5F562T7 |

0xFFFE_0000(128KB) |

0x01FFF(8KB) |

0x84000(8KB) |

JTAG/BOOT |

| |

R5F562TA |

0xFFFC_0000(256KB) |

0x03FFF(16KB) |

0x84000(8KB) |

JTAG/BOOT |

| RX62G |

R5F562G7 |

0xFFFE_0000(128KB) |

0x01FFF(8KB) |

0x84000(8KB) |

JTAG/BOOT |

| |

R5F562GA |

0xFFFC_0000(256KB) |

0x03FFF(16KB) |

0x84000(8KB) |

JTAG/BOOT |

| RX631 |

R5F56316 |

0xFFFC_0000(256KB) |

0x1FFFF(128KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F56317 |

0xFFFA_0000(384KB) |

0x1FFFF(128KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F56318 |

0xFFF8_0000(512KB) |

0x1FFFF(128KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F5631A |

0xFFF4_0000(768KB) |

0x1FFFF(128KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F5631B |

0xFFF0_0000(1.0MB) |

0x1FFFF(128KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F5631D |

0xFFE8_0000(1.5MB) |

0x1FFFF(128KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F5631E |

0xFFE0_0000(2.0MB) |

0x1FFFF(128KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F5631F |

0xFFE0_0000(2.0MB) |

0x3FFFF(256KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F5631G |

0xFFE8_0000(1.5MB) |

0x2FFFF(192KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F5631J |

0xFFE8_0000(1.5MB) |

0x3FFFF(256KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F5631K |

0xFFE0_0000(2.0MB) |

0x2FFFF(192KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F5631M |

0xFFFC_0000(256KB) |

0x0FFFF(64KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F5631N |

0xFFFA_0000(384KB) |

0x0FFFF(64KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F5631P |

0xFFF8_0000(512KB) |

0x0FFFF(64KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F5631W |

0xFFF0_0000(1.0MB) |

0x2FFFF(192KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F5631Y |

0xFFF0_0000(1.0MB) |

0x3FFFF(256KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| RX63N |

R5F563NA |

0xFFF4_0000(768KB) |

0x1FFFF(128KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F563NB |

0xFFF0_0000(1.0MB) |

0x1FFFF(128KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F563ND |

0xFFE8_0000(1.5MB) |

0x1FFFF(128KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F563NE |

0xFFE0_0000(2.0MB) |

0x1FFFF(128KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F563NF |

0xFFE0_0000(2.0MB) |

0x3FFFF(256KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F563NG |

0xFFE8_0000(1.5MB) |

0x2FFFF(192KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F563NJ |

0xFFE8_0000(1.5MB) |

0x3FFFF(256KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F563NK |

0xFFE0_0000(2.0MB) |

0x2FFFF(192KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F563NW |

0xFFF0_0000(1.0MB) |

0x2FFFF(192KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F563NY |

0xFFF0_0000(1.0MB) |

0x3FFFF(256KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| RX63T |

R5F563TB |

0xFFFC_0000(256KB) |

0x6000(24KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F563TC |

0xFFFA_0000(384KB) |

0x8000(32KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F563TE |

0xFFF8_0000(512KB) |

0xC000(48KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| RX64M |

R5F564MF |

0xFFE0_0000(2.0MB) |

0x7FFFF(512KB) |

0x84000(8KB) |

JTAG/FINE/BOOT*1 |

| |

R5F564MG |

0xFFD8_0000(2.5MB) |

0x7FFFF(512KB) |

0x84000(8KB) |

JTAG/FINE/BOOT*1 |

| |

R5F564MJ |

0xFFD0_0000(3.0MB) |

0x7FFFF(512KB) |

0x84000(8KB) |

JTAG/FINE/BOOT*1 |

| |

R5F564ML |

0xFFC0_0000(4.0MB) |

0x7FFFF(512KB) |

0x84000(8KB) |

JTAG/FINE/BOOT*1 |

| RX651 |

R5F56514 |

0xFFF8_0000(512KB) |

0x3FFFF(256KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F56517 |

0xFFF4_0000(768KB) |

0x3FFFF(256KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F56519 |

0xFFF0_0000(1.0MB) |

0x3FFFF(256KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F5651C |

0xFFE8_0000(1.5MB) |

0x3FFFF(256KB)

0x5FFFF(384KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F5651E |

0xFFE0_0000(2.0MB) |

0x3FFFF(256KB)

0x5FFFF(384KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| RX65N |

R5F565N4 |

0xFFF8_0000(512KB) |

0x3FFFF(256KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F565N7 |

0xFFF4_0000(768KB) |

0x3FFFF(256KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F565N9 |

0xFFF0_0000(1.0MB) |

0x3FFFF(256KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F565NC |

0xFFE8_0000(1.5MB) |

0x3FFFF(256KB)

0x5FFFF(384KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F565NE |

0xFFE0_0000(2.0MB) |

0x3FFFF(256KB)

0x5FFFF(384KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| RX66N |

R5F566ND |

0xFFE0_0000(2.0MB) |

0xFFFFF(1.0MB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F566NN |

0xFFC0_0000(4.0MB) |

0xFFFFF(1.0MB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| RX671 |

R5F56719 |

0xFFF0_0000(1.0MB) |

0x5FFFF(384KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F5671C |

0xFFE8_0000(1.5MB) |

0x5FFFF(384KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F5671E |

0xFFE0_0000(2.0MB) |

0x5FFFF(384KB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| RX72M |

R5F572MD |

0xFFE0_0000(2.0MB) |

0xFFFFF(1.0MB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F572MN |

0xFFC0_0000(4.0MB) |

0xFFFFF(1.0MB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| RX72N |

R5F572ND |

0xFFE0_0000(2.0MB) |

0xFFFFF(1.0MB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| |

R5F572NN |

0xFFC0_0000(4.0MB) |

0xFFFFF(1.0MB) |

0x84000(8KB) |

JTAG/FINE/BOOT |

| RX72T |

R5F572TF |

0xFFF8_0000(512KB) |

0x1FFFF(128KB) |

0x84000(8KB) |

JTAG/FINE/BOOT*1 |

| |

R5F572TK |

0xFFF0_0000(1.0MB) |

0x1FFFF(128KB) |

0x84000(8KB) |

JTAG/FINE/BOOT*1 |

| *1 |

RX64M,RX72TグループのBOOT書き込みはFROM全消去のみ対応しています。 |

|

| |

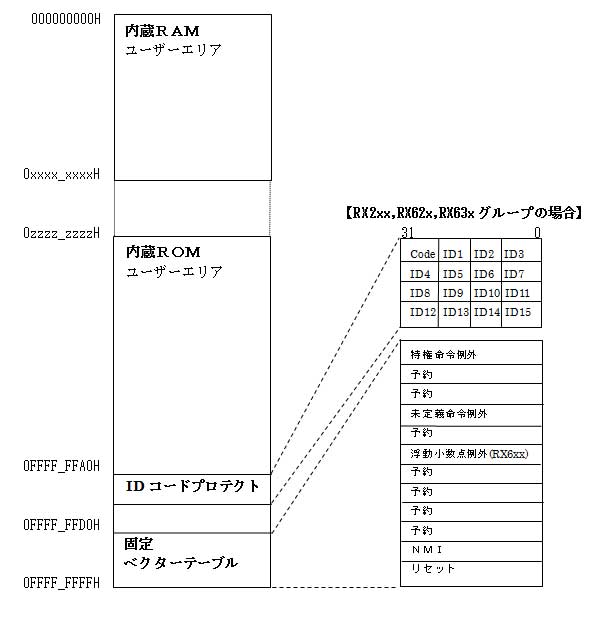

[RX2xx,RX62x,RX63xグループ]

*(long *)0xFFFF_FFA0[(char)Code,(char)ID1, (char)ID2, (char)ID3 ]

*(long *)0xFFFF_FFA4[(char)ID4, (char)ID5, (char)ID6, (char)ID7 ]

*(long *)0xFFFF_FFA8[(char)ID8, (char)ID9, (char)ID10,(char)ID11]

*(long *)0xFFFF_FFAC[(char)ID12,(char)ID13,(char)ID14,(char)ID15]

|

| |

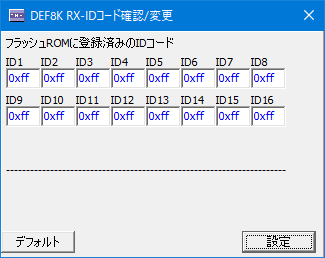

[RX64M,RX72Tグループ]

*(long *)0x0012_0050[(char)ID4, (char)ID3, (char)ID2, (char)ID1 ]

*(long *)0x0012_0054[(char)ID8, (char)ID7, (char)ID6, (char)ID5 ]

*(long *)0x0012_0058[(char)ID12,(char)ID11,(char)ID10,(char)ID9 ]

*(long *)0x0012_005C[(char)ID16,(char)ID15,(char)ID14,(char)ID13]

|

| |

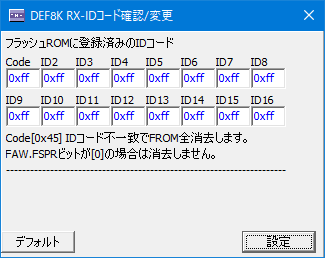

[RX651,RX65N,RX66N,RX671,RX72M,RX72Nグループ]

*(long *)0xFE7F_5D50[(char)ID4, (char)ID3, (char)ID2, (char)Code]

*(long *)0xFE7F_5D54[(char)ID8, (char)ID7, (char)ID6, (char)ID5 ]

*(long *)0xFE7F_5D58[(char)ID12,(char)ID11,(char)ID10,(char)ID9 ]

*(long *)0xFE7F_5D5C[(char)ID16,(char)ID15,(char)ID14,(char)ID13]

|

| |

2.使用制限事項

|

| ・ |

デバッグをするためには、MCUをエミュレーションモードにする必要があります。

エミュレーション−モード遷移の操作でエミュレーションモードにして下さい。 |

| ・ |

リセットベクタ値は、0x100以上にして下さい。(内蔵フラッシュROM以外の場合)

|

| ・ |

上記ファーム使用エリアは、デバッガが使用しています。ユーザはアクセスしないで下さい。

|

| ・ |

使用端子は、占有・共有使用します。(E1[14pin]に準拠)

【JTAG】(TDI TDO TCK TRST TMS)占有 (RST)共有

【FINE】(FINEC/MD0/FINED)共有 (RST)共有 [RX63xの場合]

【FINE】(MD0/FINED)共有 (RST)共有 [RX63x以外]

|

| ・ |

ターゲットとの接続は、推奨接続参考図をもとに設計して下さい。 |

| ・ |

フラッシュROMの書き換え時のSCKCRは、初期値にしています。 |

| ・ |

デバイス制限としてフラッシュメモリの書き換え回数に制限があります。 |

|

| 3.機能制限事項 |

| ・ |

ソフトウェアパーツの[PUTCH]は、使用する事が出来ません。 |

| ・ |

ソフトウェアパーツの[ソースブレーク]は、使用する事が出来ません。

|

| ・ |

フラッシュROMの書き込み回数の記憶場所を特定しない為、カウントしません。 |

|

| 4.ブレークに対する注意事項 |

| ・ |

実行前ブレーク固定です。 |

|

| 5.各MCUの特記事項 |

| 【RX2xxグループ】 |

| ・ |

FINE方式による一線式シリアルの調歩同期通信になります。 |

| ・ |

デバッガは、デバイスとの通信に内蔵の高速クロック(HOCO)を使用します。そのため、HOCOに関連するレジスタの設定に関係なくHOCOは常に発振しています。

|

| ・ |

フラッシュROMの書き換え時は、HOCO[32MHz] FCLK/1 ICLK/1 PCLKB_D/1分周に切り替えます。

|

| ・ |

HOCOの周波数切り替えとメモリアクセス動作が同時の場合、アクセス動作は不定になります。

|

| ・ |

CPU設定での内部クロック周波数は、SCKCR設定前(分周器前)の周波数を設定して下さい。 |

| ・ |

SCKCR設定後のICLKが[20MHz]未満の場合、調歩(中速)[250000BPS]以下にして下さい。 |

| ・ |

時間計測はCPU設定の周波数を元に算出します。 |

| ・ |

デバッグ操作時は、デバッグ継続モード又はLiveDebugモードを有効にするため「(long)OFS1の上位8bit[b31->b24]」を使用します。デバッグ完了時は、各モードを無効にして下さい。 |

| ・ |

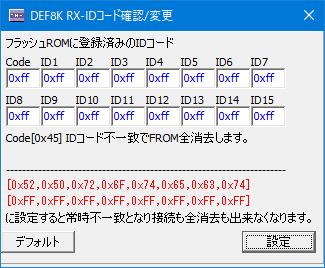

CPU設定で「BOOT」を指定する用途は、何らかの理由でIDコードが不明となりフラッシュROMを全消去する場合に使用して下さい。

ただし、Code[0x52],ID[0x50,0x72,0x6f,0x74,0x65,0x63,0x74,0xff.....0xff]を登録した場合は、エミュレーションモード遷移、及び全消去も出来なくなります。 |

| 【RX62xグループ】 |

| ・ |

デバッグ機能選択端子[EMLE]をHIGH/LOWにする場合、AH8000からのEMLE出力を利用することができます。 |

| ・ |

フラッシュROMの書き換え時は、外部発振子 ICLK*2 BCLK*2 PCLK*2に切り替えます。。 |

| ・ |

JTAGの転送クロックは、CPU設定で1MHz〜6MHzの範囲で指定して下さい。 |

| ・ |

CPU設定で「BOOT」を指定する用途は、何らかの理由でIDコードが不明となりフラッシュROMを全消去する場合に使用して下さい。

ただし、Code[0x52],ID[0x50,0x72,0x6f,0x74,0x65,0x63,0x74,0xff.....0xff]を登録した場合は、エミュレーションモード遷移、及び全消去も出来なくなります。 |

| 【RX63xグループ】 |

| ・ |

デバッグ機能選択端子[EMLE]をHIGH/LOWにする場合、AH8000からのEMLE出力を利用することができます。 |

| ・ |

フラッシュROMの書き換え時は、HOCO[50MHz] FCLK/2 ICLK/1 BCLK/stop PCLK/2分周に切り替えます。 |

| ・ |

【RX63T】フラッシュROMの書き換え時は、外部発振子 FCLK*4 ICLK*8に切り替えます。 |

| ・ |

JTAGの転送クロックは、CPU設定で1MHz〜6MHzの範囲で指定して下さい。 |

| ・ |

このグループは、リセット解除時に低速オシレータLOCO[125KHz]に切り替わります。 |

| ・ |

CPU設定でのシステムクロック(Iclk)は、SCKCR設定後の動作周波数を設定して下さい。 |

| ・ |

時間計測はCPU設定の周波数を元に算出します。 |

| ・ |

【FINE】デバッグ操作時は、デバッグ継続モード又はLiveDebugモードを有効にするため「(long)OFS1の上位8bit[b31->b24]」を使用します。デバッグ完了時は、各モードを無効にして下さい。 |

| ・ |

CPU設定で「BOOT」を指定する用途は、何らかの理由でIDコードが不明となりフラッシュROMを全消去する場合に使用して下さい。

ただし、Code[0x52],ID[0x50,0x72,0x6f,0x74,0x65,0x63,0x74,0xff.....0xff]を登録した場合は、エミュレーションモード遷移、及び全消去も出来なくなります。 |

| 【RX64M,RX72Tグループ】 |

| ・ |

デバッグ機能選択端子[EMLE]をHIGH/LOWにする場合、AH8000からのEMLE出力を利用することができます。 |

| ・ |

フラッシュROMの書き換え時は、HOCO[16MH] FCLK/1 ICLK/1 BCLK/stop PCLKx/1分周に切り替えます。 |

| ・ |

SPCC(*(long)0x0012_0040)の設定は、仕様を理解した上で設定して下さい。デタラメな数値を設定すると二度と書き換え出来なくなります。 |

| ・ |

このグループは、リセット解除時に低速オシレータLOCO[240KHz]に切り替わります。 |

| ・ |

CPU設定でのシステムクロック(Iclk)は、SCKCR設定後の動作周波数を設定して下さい。 |

| ・ |

時間計測はCPU設定の周波数を元に算出します。 |

| ・ |

【FINE】デバッグ操作時は、デバッグ継続モード又はLiveDebugモードを有効にするため「(long)OFS1の上位8bit[b31->b24]」を使用します。デバッグ完了時は、各モードを無効にして下さい。 |

| ・ |

CPU設定で「BOOT」を指定する用途は、何らかの理由でIDコードが不明となりフラッシュROMを全消去する場合に使用して下さい。

オプション設定メモリの一部は消去できないビットがあります。、 |

| 【RX651,RX65N,RX66N,RX671,RX72M,RX72Nグループ】 |

| ・ |

デバッグ機能選択端子[EMLE]をHIGH/LOWにする場合、AH8000からのEMLE出力を利用することができます。 |

| ・ |

フラッシュROMの書き換え時は、HOCO[16MHz] FCLK/1 ICLK/1 BCLK/stop PCLKx/1分周に切り替えます。 |

| ・ |

SPCC(*(long)0xFE7F5D40)の設定は、仕様を理解した上で設定して下さい。デタラメな数値を設定すると二度と書き換え出来なくなります。 |

| ・ |

このグループは、リセット解除時に低速オシレータLOCO[240KHz]に切り替わります。 |

| ・ |

CPU設定でのシステムクロック(Iclk)は、SCKCR設定後の動作周波数を設定して下さい。 |

| ・ |

時間計測はCPU設定の周波数を元に算出します。 |

| ・ |

【FINE】デバッグ操作時は、デバッグ継続モード又はLiveDebugモードを有効にするため「(long)OFS1の上位8bit[b31->b24]」を使用します。デバッグ完了時は、各モードを無効にして下さい。 |

| ・ |

CPU設定で「BOOT」を指定する用途は、何らかの理由でIDコードが不明となりフラッシュROMを全消去する場合に使用して下さい。

ただし、制御コード[0x45]とFAW.FSPR[1]の場合に限り全消去可能となりますが、オプション設定メモリの一部は消去できないビットがあります。 |

| |

| 6.ファーム起動時のMCUに対する設定 |

| ・ |

特にありません。 |

|

| 7.低消費電力モード状態の注意事項 |

| ・ |

低消費電力状態でブレーク発行にて低消費電力モードは解除されます。 |

|

| 8.ウォッチドッグタイマの注意事項 |

| ・ |

レジスタスタートモードの場合は、特に制限事項ありません。 |

| ・ |

【RX2xxグループ】

デバッグ継続モード無効時は、OFS0を使用したオートスタートモードの指定が反映されないため確認できません。 |

|

| 9.その他の注意事項 |

| ・ |

RX内部I/Oレジスタの中には、16,32ビットの指定ビットによるアクセス制限がついている場合があります。メモリセットコマンド等で内部I/Oレジスタアクセスする場合は、指定ビット長でアクセスして下さい。指定外ビット長でアクセスしますと間違った情報を得ることになります。 |

|

| 10.オンザフライ時のMCU停止時間の計測値 |

| 品種 |

RX62x/63x/64x/65x/66x/67x/72x |

RX21x/23x |

| コマンド |

停止時間 単位(msec) |

停止時間 単位(msec) |

| CPU設定 |

− |

− |

| デバッグI/F |

JTAG |

FINE |

| 割込み方式 |

− |

− |

| 割込みが使用できる条件 |

− |

− |

| 1バイトのメモリアクセス |

0.00(NonStop)

バイト数に影響されない |

0.00(NonStop)

バイト数に影響されない |

| 全レジスタ |

20.0 |

40.0 |

| 個別レジスタ(Rレジスタ) |

1.00 |

2.00 |

| 個別レジスタ(PSWレジスタ) |

0.00(NonStop) |

0.00(NonStop) |

| 個別レジスタ(PCレジスタ) |

0.00(NonStop) |

0.00(NonStop) |

| 1行の逆アセンブラ |

0.00(NonStop) |

0.00(NonStop) |

| DI,EI.IntFlg(割込み系) |

10.0 |

10.0 |

| ブレークポイントの設定 |

20.0 |

20.0 |

| ブレークポイントの解除 |

20.0 |

20.0 |

| 停止時間の計測方法 |

計測方法なし |

計測方法なし |

*RX62N クロックが12.000x8MHz時の実測値

*RX210 クロック(HOCO)が50.000MHz時の実測値

|

<オンザフライ機能使用時の注意事項 メモリアクセス以外の場合>

|

| ・ |

BP(ブレークポイント)を張ってる状態で、オンザフライの自動実行とBP停止が同時に発生した場合、自動実行側が優先されます。 |

|